什么是RISC-V?

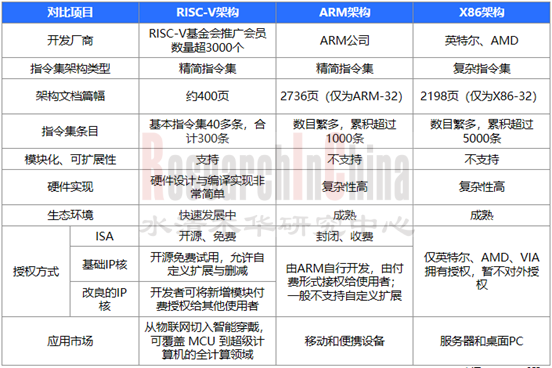

RISC-V(Reduced Instruction Set Computing - Five),中文名为第五代精简指令集。它是一种基于精简指令集原则的开源指令集架构(ISA),可用于设计和实现处理器芯片和计算机体系结构。它是全球共识的第三大架构,与X86和ARM并列。

其优势主要在于RISC-V的指令集和架构是开源免费的。其模块化设计允许企业添加、拓展或移除指令集。与之相比,ARM与X86不仅指令集开发复杂,且难以获得修改指令集授权。

其劣势主要在于生态系统相对不够成熟。相关的编译器、开发工具和软件开发环境(IDE)及其它生态要素还在发展。

RISC-V与X86、ARM架构对比

来源:RISC-V手册

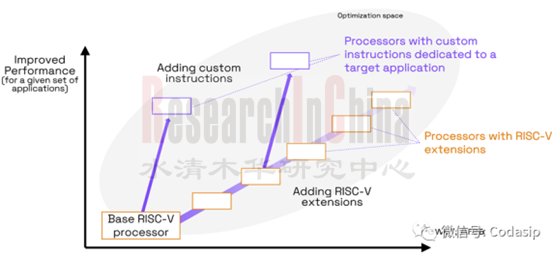

RISC-V使芯片定制化更容易

RISC-V采用模块化 ISA,即由 1 个基本整数指令集(基本整数指令集是RISC-V唯一强制要求实现的基础指令集,其他指令集都是可选的扩展模块) + 多个可选的扩展指令集组成。因此可根据应用程序的需求定制CPU。

其定制化优势在于它使设计人员能够创建数千个潜在的定制处理器,从而加快上市时间。处理器IP的通用性还节省了软件开发时间。

RISC-V定制化的主要优势

来源:Codasip

例如,Codasip可为用户提供基于RISC-V架构的处理器IP定制解决方案。该方案包括基础性的处理器IP和开发工具Codasip Studio。工程团队能够针对其项目需求实现硬件和软件一体化设计,提升定制化处理器设计的效率。Codasip还于2023年10月推出了用于定制计算的700系列处理器。借助700系列和Codasip的定制计算,设计人员可通过在芯片或应用层面进行优化,获得独特的收益,同时控制成本。

SiFive也是基于 RISC-V 定制化的半导体企业。SiFive的主业是基于RISC-V架构帮助企业定制处理器内核。通过其定制化RISC-V半导体产品,帮助IC设计及系统公司缩短上市时间,减少成本费用。

2022年已出货100亿颗,RISC-V向高性能领域拓展

据RISC-V基金会数据,2022年采用RISC-V芯片架构的处理器核已出货100亿颗,主要用于物联网领域。随着市场需求的增长,RISC-V也开始逐渐走向高性能领域。例如自动驾驶、人工智能、通信、数据中心等对算力要求更高的场景。

特斯拉于2021年自研定制化芯片“D1”。D1以RISC-V架构ISA为基础进行扩展,可训练数据中心内部的人工智能网络。

Mobileye(被Intel收购)也于2022年1月发布12核RISC-V自动驾驶芯片EyeQ Ultra,其CPU内核全部用的是RISC-V。预计2025年量产。

2023年9月,赛昉科技(StarFive)发布高性能RISC-V CPU IP——昉·天枢-90(Dubhe-90)。Dubhe-90是Dubhe Max Performance系列旗舰产品,SPECint2006 9.4/GHz,性能比肩ARM Cortex-A76,客户主要来自于PC、高性能网络通讯、机器学习、数据中心等高端应用领域。

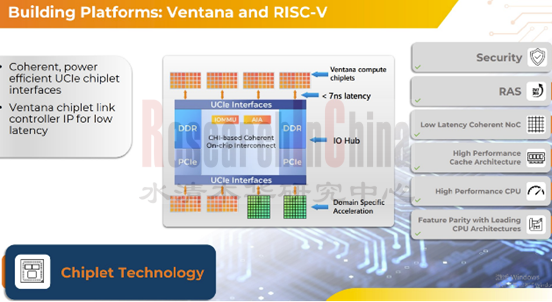

RISC-V与Chiplet技术结合,降低芯片设计成本及门槛

为降低芯片设计成本及门槛,RISC-V处理器开发公司及研究机构还将RISC-V与Chiplet技术结合。

Chiplet,中文叫芯粒,是将特定功能的裸片(die),通过芯片内互联技术(die-to-die)实现多个同质、异构的模块芯片封装在一起。Chiplet技术可将系统级芯片分割成独立的模块,进行单独制造,从而改善良率,降低设计成本。

芯片设计领域初创公司Ventana Micro Systems于2023年11月推出第二代 Veyron 系列基处理器—Veyron V2。Veyron V2基于RISC-V架构处理器开发,以Chiplet和 IP 的形式进行提供。Veyron V2 chiplet采用UCIe chiplet互连,可将处理器上市时间缩短两年,并将开发成本降低75%。基于chiplet的解决方案还通过调整计算、I/O和内存的大小来提供更好的单元经济性。

Ventana将RISC-V与Chiplet技术结合

来源:Ventana

芯来科技,作为RISC-V架构CPU IP企业,也在布局Chiplet。2022年11月,芯来科技加入UCIe(Universal Chiplet Interconnect Express)产业联盟,成为UCIe联盟新成员。作为中国国内首批加入该联盟的RISC-V CPU IP企业。芯来科技将与UCIe产业联盟全球范围内其他成员共同致力于UCIe 1.0版本规范和下一代UCIe技术标准的研究与应用,并将开展基于Chiplet互联的硬核IP研发。

2024年1 月 9 日,中国科学院计算技术研究所也推出了一种名为“Zhejiang”(浙江)的“大芯片”。采用 Chiplet 设计,共包括 16 个Chiplets,而每个Chiplet内有 16 个 RISC-V 核心,总计 256 核心,且均支持可编程、可重新配置。

国产替代空间大,汽车电子市场有望成为RISC-V下一爆发点

一辆汽车中所使用的半导体器件数量中,MCU占比约30%。传统汽车约有50-100个MCU,智能汽车MCU数量将翻倍。而国产车规MCU领域市占率不足5% ,国产替代空间较大。

以往车载芯片主要基于ARM架构或欧洲一些芯片公司的私有架构。RISC-V开放架构的出现为国产车载芯片的研发提供更广阔的选择面。其开放性设计使得汽车芯片厂商可根据自身的需求进行特性布局,从而丰富产品形态。

近几年来,已有不少国内车规级MCU厂商选择RISC-V架构来打造自己的MCU,包括武汉二进制、国芯科技、凌思微、芯科集成等。

其中,国芯科技将探索RISC-V架构在汽车电子中高端MCU芯片中的应用。如面向新能源动力域OBC/DC-DC应用的CCFC3010PT芯片,这是国芯科技首款基于RISC-V指令架构的车规MCU芯片。同时,将启动开发CCFC3009PT芯片,这是面向自驾领域设计开发的MCU芯片,主要面向ISP及毫米波雷达信号的后处理。

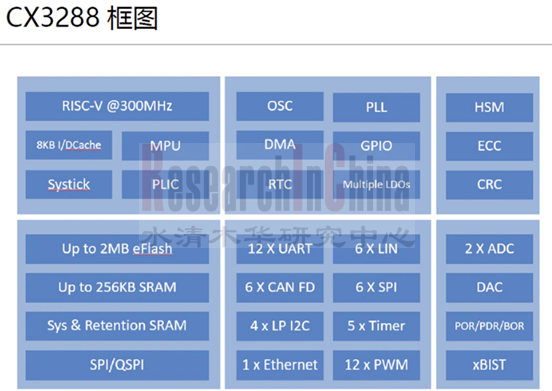

芯科集成于2023年8月推出的车规级MCU CX3288采用32位RISC-V内核,符合功能安全ISO26262 ASIL-B的要求,在信息和网络安全方面支持SHE(安全硬件扩展)、Medium HSM,支持通信加密和安全启动。并且支持AutoSAR,可提供MCAL和配置工具支持。

国内MCU厂商布局车用RISC-V领域

来源:《2024年车用RISC-V芯片产业研究报告》

芯科集成推出基于RISC-V的车规MCU

来源:芯科集成

当前汽车软件和工具链仍比较碎片化,若使用 ARM 一个架构适用于所有情况,那么从上层软件厂商和操作系统到应用程序厂商都很难找到通用性。相比ARM,RISC-V的定制能力较强,其丰富的延展性可满足未来汽车电子系统不断增长的需求;且该架构免费使用,可降低研发成本,不受任何专利或版权制约。因此,汽车电子有望成为RISC-V下一个爆发点。

面向RISC-V在汽车电子的发展机遇,2023年12 月,高通、博世、英飞凌、恩智浦、北欧半导体(Nordic)等五家头部汽车电子芯片公司共同投资组建了一家专注于 RISC-V 生态的初创企业 ——Quintauris。公司总部位于德国慕尼黑,CEO 为Alexander Kocher,(此前曾担任汽车嵌入式方案供应商 Elektrobit 的 CEO 兼总裁,还曾在大陆集团、西门子和英飞凌等公司任职)。公司创立初期将重点针对汽车应用,随后逐步扩展到移动设备、物联网芯片等领域。

高通联合其他四家企业成立RISC-V 生态企业

来源:Quintauris

但在RISC-V上车方面需面临两大挑战。一是“车规”认证周期长;首先,需通过16949认证,芯片需要获得ACQ-100认证,模组需要获得ACQ-104认证,同时还需通过功能安全ISO26262认证。二是需建立健全的软件生态。包括更广泛的操作系统和中间件支持,及更多针对特定汽车应用的优化和验证。

国内主机厂支持RISC-V发展,积极与国内芯片厂商合作

一些国内主机厂也对RISC-V持欢迎态度,正积极与国内芯片厂商合作。例如东风汽车、比亚迪、奇瑞等。

2022年5月,东风公司牵头联合中国信科、武汉菱电、武汉理工、华中科大、芯来科技、泰晶科技等8家单位启动共建“湖北省车规级芯片产业技术创新联合体”。

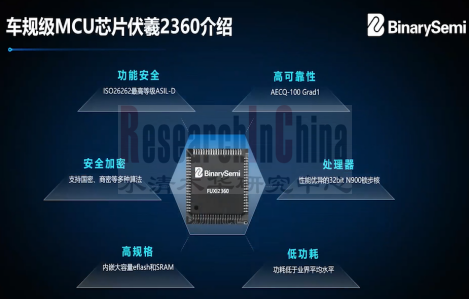

2022年12月,由东风汽车旗下基金参投的武汉二进制半导体发布基于RISC-V架构的高性能车规级MCU芯片伏羲2360,采用芯来科技NA900 RISC-V 多核异构CPU IP。可用于发动机、变速箱、三电控制、ADAS、整车控制等领域。

车规级MCU芯片伏羲2360

来源:武汉二进制半导体

2023年7月,东风公司宣布,由其牵头成立的湖北省车规级芯片产业技术创新联合体已实现3款国内空白车规级芯片首次流片(试生产),完成了国内首款基于RISC-V指令集架构车规级MCU芯片。

奇瑞也在与国内芯片厂商合作,来定义整个RISC-V的测试架构,例如在基于RISC-V的客户端和RISC-V芯片的测试标准,来确保RISC-V芯片的可靠性。除芯片测试之外,奇瑞还基于车规,如AEC-Q100,进行了安全可靠性的测试。

此外,比亚迪与华为合作,双方在基于RISC-V架构的英特尔或高通的芯片上联合开展研究。

1 RISC-V架构如何突出重围?

1.1 RISC-V定义及发展历程

1.2 RISC-V发展里程碑

1.3 指令集分类

1.4 三大主流芯片架构RISC-V与ARM、X86对比

1.4.1 RISC-V与ARM架构区别

1.4.2 RISC-V与ARM优劣势对比

1.4.3 RISC-V与ARM、X86商业模式对比

1.5 RISC-V主要落地场景

1.5.1 汽车电子有望成为RISC-V下一爆发点

1.5.2 RISC-V处理器在车载场景应用的优劣势

1.5.3 RISC-V在车载MCU操作系统的应用机会

1.5.4 RISC-V在座舱SoC操作系统的应用机会

1.5.5 RISC-V在座舱SoC操作系统的应用案例

1.5.6 RISC-V在智驾SoC操作系统的应用机会

1.5.7 RISC-V在汽车芯片中的应用案例(1)

1.5.7 RISC-V在汽车芯片中的应用案例(2)

1.5.7 RISC-V在汽车芯片中的应用案例(3)

1.5.7 RISC-V在汽车芯片中的应用案例(4)

1.6 RISC-V上车挑战(1)

1.6.1 RISC-V厂商获汽车功能安全认证案例

1.6 RISC-V上车挑战(2)

1.6 RISC-V上车挑战(3)

1.6 RISC-V上车挑战(4)

1.7 如何推动 RISC-V 产业化落地?

1.7.1 各国政府出台政策支持RISC-V发展及商业化-国外政府

1.7.2 各国政府出台政策支持RISC-V发展及商业化-中国政府

1.7.3 RISC-V五种商业模式分析

1.7.3.1 模式一

1.7.3.2 模式二

1.7.3.2.1 案例一

1.7.3.2.2 案例二

1.7.3.2.3 案例三

1.7.3.3 模式三

1.7.3.4 模式四

1.7.3.5 模式五

1.8 如何降低开源芯片开发门槛?

1.8.1 构建开源芯片生态,降低芯片设计成本

1.8.2 构建自主开源芯片生态的三步走规划

1.8.3 开源芯片开发模式及流程探索

1.8.3.1 开源芯片开发流程探索-面向对象芯片设计方法

1.8.3.2 开源芯片开发流程探索-建立一套敏捷验证平台

1.8.3.3 开源芯片开发流程探索-探索基于开源众包的验证

1.8.3.4 开源芯片开发流程探索-开源EDA工具链

1.8.4 开源标准下的行业格局:RISC-V三大类玩家

2 RISC-V车规级产品及市场趋势

2.1 RISC-V市场出货量趋势

2.1.1 主要车用RISC-V CPU IP及芯片厂商产品汇总(1)

2.1.1 主要车用RISC-V CPU IP及芯片厂商产品汇总(2)

2.2 趋势一

2.3 趋势二

2.4 趋势三

2.4.1 案例一

2.4.2 案例二

2.4.3 案例三

2.4.4 案例四

2.4.5 案例五

2.4.6 全球业界对高性能RISC-V芯片关键节点的期待

2.5 趋势四

2.6 趋势五

2.7 趋势六

2.7.1 案例一

2.7.2 案例二

2.7.3 案例三

2.8 趋势七

2.8.1 案例一

2.8.2 案例二

2.9 趋势探讨:RISC-V是否会取代X86 和 ARM架构?

2.9.1 全球CPU指令集发展方向

2.10 趋势探讨:RISC-V架构兴起,将是国产汽车芯片厂商的突破口?

2.10.1 车规MCU现状和趋势:汽车MCU市场内核架构的多元化

2.10.2 RISC-V汽车芯片在中国市场的发展机遇

2.10.3 不少国内MCU厂商选择RISC-V架构打造车规级MCU

2.10.4 中国芯片产业合作动态

3 车用RISC-V CPU IP及芯片厂商

3.1 芯来科技

3.1.1 芯来科技简介

3.1.2 RISC-V CPU IP产品矩阵

3.1.3 NA车规系列CPU IP 获ISO 26262 ASIL-D认证

3.1.4 NA车规系列提供ASIL B和ASIL D的两种功能安全等级方案

3.1.5 NA车规系列CPU IP NA900 & NA300及其安全机制对比

3.1.6 NA车规系列支持双核锁步模式

3.1.7 NA车规系列客户案例

3.1.8 NA车规系列CPU IP未来规划

3.1.9 芯来科技RISC-V软件开发平台

3.1.10 芯来科技与IAR合作

3.2 Andes晶心科技

3.2.1 晶心科技简介

3.2.2 晶心科技RISC-V CPU核心产品矩阵

3.2.3 晶心科技RISC-V CPU IP汽车功能安全发展历程

3.2.4 AndesCore ISO 26262功能安全系列产品路线图

3.2.5 车用RISC-V CPU核心 AndesCore™ D25F-SE主要特点

3.2.6 车用RISC-V CPU核心AndesCore™ D45-SE主要特点

3.2.7 晶心科技车用RISC-V CPU核心客户案例

3.2.8 晶心科技汽车生态系统

3.2.9 晶心科技汽车生态合作动态

3.3 ESWIN奕斯伟

3.3.1 奕斯伟简介

3.3.2 奕斯伟以RISC-V为基础的产品矩阵

3.3.3 奕斯伟 RISC-V 全系列CPU IP

3.3.4 奕斯伟车载业务布局

3.3.5 奕斯伟自研RISC-V 处理器在车载场景的产品路线图

3.3.6 奕斯伟32位RISC-V车规级CPU IP产品 E302A架构

3.3.7 奕斯伟32位RISC-V车规级CPU IP产品 E320A架构

3.3.8 奕斯伟32位RISC-V车规级CPU IP产品 E330A架构

3.3.9 奕斯伟32位RISC-V车规级CPU IP产品 S500A架构

3.3.10 奕斯伟自研国产工艺平台RISC-V MCU

3.3.11 奕斯伟自研国产工艺平台RISC-V MCU功能安全架构

3.3.12 奕斯伟自研国产工艺平台RISC-V MCU故障活动及安全分析的实现

3.3.13 奕斯伟基于RISC-V处理器的车规级MCU完整软件栈

3.4 SiFive

3.4.1 SiFive简介

3.4.2 SiFive基于RISC-V的处理器内核产品矩阵

3.4.3 SiFive Automotive系列RISC-V内核IP路线图

3.4.4 SiFive 车用处理器内核P870-A主要特点

3.4.5 SiFive 车用处理器内核P870-A架构特性

3.4.6 SiFive汽车生态系统

3.4.7 SiFive汽车领域合作动态

3.5 Codasip

3.5.1 Codasip简介

3.5.2 Codasip RISC-V基准处理器产品矩阵

3.5.3 Codasip RISC-V CPU L31架构

3.5.4 EDA工具Codasip Studio

3.5.5 Codasip 商业模式-提供IP定制化解决方案

3.6 RAMBUS

3.6.1 Rambus提供基于RISC-V设计的硬件安全内核

3.6.2 Rambus针对汽车应用的安全协处理器RT-645

3.6.3 Rambus 信任根 RT-640 嵌入式硬件安全模块(HSM)

3.7 瑞萨电子

3.7.1 瑞萨电子下一代MCU与片上系统(SoC)解决方案路线图:将支持Chiplet技术

3.7.2 瑞萨电子第四代汽车MCU RH850/U2B采用RISC-V内核

3.7.3 瑞萨RH850/U2B汽车MCU内部框架

3.8 Tenstorrent

3.8.1 Tenstorrent简介

3.8.2 Tenstorrent芯片路线图

3.8.3 Tenstorrent RISC-V处理器产品矩阵

3.8.4 Tenstorrent商业模式

3.8.5 Tenstorrent为汽车开发专用芯片合作案例

3.9 Kneron

3.9.1 Kneron引入基于RISC-V的汽车AI边缘芯片(1)

3.9.2 Kneron引入基于RISC-V的汽车AI边缘芯片(2)

3.9.3 Kneron引入基于RISC-V的汽车AI边缘芯片(3)

3.10 芯科集成

3.10.1 芯科集成简介

3.10.2 芯科集成的MCU解决方案

3.10.3 芯科集成推出基于RISC-V的车规MCU

3.11 隼瞻科技

3.11.1 隼瞻科技简介

3.11.2 隼瞻科技车规级RISC-V IP产品Roadmap

3.11.3 隼瞻科技车规级RISC-V IP产品Wing-M500主要特点

3.11.4 隼瞻科技商业模式

3.11.5 隼瞻自研WingStudio敏捷开发平台降低专用处理器设计门槛

3.12 Mobileye

3.12.1 Mobileye EyeQ系列芯片发展路线图

3.12.2 Mobileye基于开源 RISC-V 架构的处理器EyeQUltra架构图

3.12.3 Mobiley发布基于开源 RISC-V 架构的处理器EyeQUltra

3.13 二进制半导体

3.13.1 二进制半导体简介

3.13.2 车规MCU芯片及RISC-V内核芯片规划

3.13.3 车规级MCU芯片伏羲2360基于RISC-V内核(1)

3.13.4 车规级MCU芯片伏羲2360基于RISC-V内核(2)

3.13.5 二进制半导体构建汽车芯片生态应用

3.14 方寸微电子

3.14.1 方寸微电子简介

3.14.2 车规级安全MPU芯片方寸T690架构框图

3.14.3 车规级安全MPU芯片方寸T690搭载完善SDK

3.14.4 车规级安全MPU芯片方寸T690 HSM及网络子系统

3.15 泰凌微电子

3.15.1 泰凌微电子简介

3.15.2 泰凌微电子产品阵容

3.15.3 基于RISC-V架构的车规级无线MCU产品TLSR9架构

3.15.4 泰凌微电子提供完整的自研协议栈加快产品上市

3.16 先楫半导体

3.16.1 先楫半导体简介

3.16.2 HPM6000系列RISC-V通用MCU产品主要特点

3.16.3 先楫半导体工业及车规MCU产品路线图

3.16.4 基于RISC-V内核的汽车级MCU HPM64A0系统架构框图

3.16.5 基于RISC-V内核的汽车级MCU HPM64A0应用案例

3.16.6 先楫半导体为开发者提供完备生态系统

3.17 凌思微

3.17.1 凌思微简介及无线MCU产品布局

3.17.2 凌思微电子基于RISC-V架构的车规级无线MCU产品

3.18 NSITEXE

3.18.1 NSITEXE推出RISC-V数据流处理器IP

3.18.2 NSITEXE推出RISC-V CPU

4 RISC-V生态软件厂商(汽车领域)

4.1 IAR

4.1.1 IAR简介

4.1.2 IAR开发工具链IAR Embedded Workbench for RISC-V主要特点

4.1.3 IAR开发工具链IAR Embedded Workbench for RISC-V迭代历程

4.1.4 IAR开发工具链IAR Embedded Workbench for RISC-V通过功能安全认证

4.1.5 RISC-V功能安全应用案例(车用领域)

4.2 智达诚远

4.2.1 智达诚远简介

4.2.2 智达诚远核心产品

4.2.3 智达诚远基于RISC-V架构在操作系统的发展

4.3 Green Hills Software

4.3.1 Green Hills Software实时操作系统µ- veloSity RTOS支持RISC-V架构

4.3.2 Green Hills Software RISC-V相关合作动态

4.4 Vector与Andes合力推动车用产业RISC-V AUTOSAR软件创新